Общие сведения об информации

| 1.1. Общие сведения об информации

Цифровые устройства являются составной частью всех ЭВМ, систем автоматического управления, автоматизированного управления и предназначены для обработки, хранения и передачи дискретной (цифровой) информации. В узком смысле слова информация - отражение реального мира. С точки зрения связистов и электронщиков – информация - это любые сведения, являющиеся объектом хранения, передачи и преобразования. Информацию, воплощенную и зафиксированную в некоторой материальной форме, называют сообщением и передают с помощью сигналов. Сигналом могут служить любые физические явления или объекты, изменение параметров которых во времени несет информацию в прямом или закодированном виде (свет, звук, напряжение, ток, давление, и т.д.). В общем случае информационное сообщение может быть представлено в виде функции x(t). Причем эта функция может принимать любые вещественные значения в диапазоне изменения аргумента t. Например, изменение температуры во времени и т.д.

Классы сигналов. Среди множества сигналов можно выделить два типа сигналов, используемых для передачи, обработки и хранения информации. Это аналоговый и дискретный сигналы. Аналоговым называется сигнал, определенный для любого момента времени. Дискретным называется сигнал, определенный только в дискретные моменты времени, например, через одну мсек. и т.д. Каждое значение дискретного сигнала может быть представлено числом любой приемлемой системы счисления. В цифровых системах представление дискретных значений сигнала числом, называется кодированием. Кодирование чаще всего производится числами двоичной системы счисления.

Значение кодированного числа, представленное в привычной для нас десятичной системе счисления, определяет число уровней (Кn) квантования, т.е. дискретизации (рис. 1.2). Шаг квантования (дискретизации) определяется как  Число разрядов двоичного числа m, соответствующего Кn, определяется как  т.е. как целая часть логарифма максимального значения числа Кnmax, дополненного единицей. |

Основы алгебры логики

| 1.4. Основы алгебры логики

Алгебра логики (АЛ) является основным инструментом синтеза и анализа дискретных автоматов всех уровней. АЛ называют также Булевой алгеброй. АЛ базируется на трёх функциях, определяющих три основные логические операции. 1. Функция отрицания (НЕ). f1 =`X читается, как f1 есть (эквивалентна) НЕ Х. Элемент, реализующий функцию НЕ, называется элементом НЕ (инвертором).

2. Функция логического умножения (конъюнкции). Функция логического умножения записывается в виде f2=X1·X2. Символы логического умножения &, L, <×>, ´. Функция конъюнкции читается так: f2 есть (эквивалентна) Х1 и Х2, поскольку функция истинна тогда, когда истинны 1-й и 2-й аргументы (переменные). Конъюнкцию называют функцией И, элемент, реализующий эту функцию, элементом И.

В общем случае функцию логического умножения от n переменных записывают так:

Количество переменных (аргументов), участвующих в одной конъюнкции, соответствует количеству входов элемента И. 3. Логическое сложение (дизъюнкция). Функция логического сложения записывается в виде f3=X1 + X2, и читается так: f3 есть Х1 или Х2, поскольку функция истинна, когда истинна одна или другая переменная (хотя бы одна). Поэтому функцию дизъюнкции часто называют функцией ИЛИ. Символы логического сложения +,V. В общем случае функция ИЛИ записывается:

Используя операции (функции) И, ИЛИ, НЕ можно описать поведение любого комбинационного устройства, задав сколь угодно сложное булево выражение. Любое булево выражение состоит из булевых констант и переменных, связанных операциями И, ИЛИ, НЕ. Пример булева выражения:

Основные законы алгебры логики. Основные законы АЛ позволяют проводить эквивалентные преобразования функций, записанных с помощью операций И, ИЛИ, НЕ, приводить их к удобному для дальнейшего использования виду и упрощать запись. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Таблица 1.1

Используя законы алгебры логики, можно упростить булевы выражения, в частности, правило склеивания позволяет упростить выражение типа  Действительно, используя законы 2, 5 и 11 можно записать исходное выражение в виде Х2(Х1 +`Х1 ) =Х2. Так как логическая операция Х1 +`Х1 = 1 (см. з-н 5), а Х2×1 = Х2 (см. з-н 2б), полученное выражение истинно. Способы задания функций алгебры логики. При сопоставлении функций АЛ с дискретными автоматами аргументы функций, сопоставляются с входами, а сами функции с выходами дискретного автомата. Поскольку дискретный автомат имеет конечное число входов, то мы будем иметь дело с функцией конечного числа аргументов. Если автомат имеет m входов, то количество входных переменных тоже m и число возможных комбинаций наборов значений этих входных аргументов (переменных) К=2m. Поскольку автомат имеет конечное число входов, его состояние описывается конечным числом значений функций выходов. Существует несколько способов задания функций АЛ и дискретного автомата. 1. Табличный способ. При этом способе функция задается в виде таблицы истинности, представляющей собой совокупность всех наборов переменных и соответствующих им значений функции. Таблица истинности содержит 2m строк, m столбцов (по количеству входов) и один столбец для записи значения функции. Например: пусть требуется задать функцию трех переменных F1(Х1,Х2,Х3) (рис. 1.4), т.е. автомат на три входа и на один выход, следовательно, M=3, К=8.

Следующий способ задания дискретного автомата – числовой. В Этом случае функция задается в виде десятичных эквивалентов номеров наборов аргументов, при которых функция принимает единичное значение. Например, для рассмотренного выше примера функция F1 принимает единичные значения на наборах переменных со следующими номерами: 1, 2, 5, тогда числовой способ задания будет иметь вид  Координатный способ. При этом способе дискретный автомат задается с помощью карты его состояния, которая известна как карта Карно. Карта Карно содержит 2m клеток по числу наборов значений переменных. Каждая клетка определяется координатами строк и столбцов, соответствующими определенному набору переменных. Все входные переменные разбиваются на 2 группы так, что одна группа определяет координаты строк, а другая - координаты столбцов. В каждой клетке карты Карно проставляется соответствующее значение функции на заданном наборе. Пример задания функции трех переменных приведен на рис. 1.5. Числовое выражение этой функции выглядит так:

Пусть функция задана в числовой форме и имеет вид:  следовательно, К=16, m=4. Сначала проводим разметку координат карты Карно без указания значений функции. Для удобства воспользуемся указанием "шапки" в виде прямых линий, “под” которыми переменные входят в значение координат без отрицания (рис.1.6). Таким образом, по столбцам и по строкам переменные входят без отрицания в пределах линии-шапки.

Для наглядности координаты клеток карты Карно указаны в трех формах: в виде наборов переменных; в виде двоичного числа, соответствующего порядковому номеру набора переменных; в десятичном эквиваленте номеров наборов переменных. На практике координаты внутри клеток не записывают (рис. 1.7), в клетках указываются единичные значения функции, соответствующие “координатным” наборам переменных. Нулевые значения функции в клетки можно не записывать, т.е. клетки, координаты которых определяются наборами переменных с нулевыми значениями функции, можно оставить пустыми.  Следует отметить, что перестановка местами переменных Х1 и Х2, а так же переменных Х3 и Х4 допускается, допускается также перестановка местами переменных Х1Х2 и Х4Х3. При построении карты Карно, т.е. при задании логической функции, указывают лишь внешние элементы разметки координат (рис. 1.7). Аналитический способ задания функции алгебры логики. При этом способе функция задается в виде аналитического выражения, полученного путем применения каких-либо логических операций. Например:  Совершенная нормальная дизъюнктивная форма (СНДФ). По таблице истинности можно составить логическое выражение, содержащее наборы переменных, в которые входят все переменные с отрицанием или без. Одна из его форм называется СНДФ. В качестве примера получения СНДФ рассмотрим случай задания логической функции в виде таблицы истинности. Пусть задана функция трех переменных. Таблица истинности этой функции показана на рис. 1.8. (очевидно, что значения функции взяты произвольно и могут быть любыми).

Из таблицы истинности видно, что функция принимает значение логической единицы только на трех наборах переменных, т.е. на 2, 4 и 5-м наборах. Для второй строки (второго набора переменных) можно записать: Х1=0, Х2=1, Х3=0, следовательно, функция f(0,1,0)=1. Принято (по умолчанию) считать, что если переменная в "нормальном" состоянии имеет значение логической единицы, а в инверсном - логического нуля, тогда функцию для второй строки можно представить в виде `X1Х2X3 = 1. Для четвертой строки - `X1X2Х3 = 1 и для пятой строки - Х1X2Х3 = 1. Аналитическое выражение функции выглядит как  Каждое произведение содержит все три переменные с отрицанием или без отрицания и соответствует только одной строке набора переменных, на котором функция принимает значение логической единицы. Произведения, в которых содержатся все переменные с отрицанием или без, называются конституентами единицы или минтермами. Функция будет представлять логическую сумму всех произведений, равных логической единице. В нашем примере вся сумма (дизъюнкция) соответствует совокупности произведений переменных для трех строк. СНДФ любой функции записывается по таблице истинности согласно следующему правилу. Для каждого набора переменных, на которых функция принимает значение логической 1, записываются конституенты, и все эти конституенты объединяются дизъюнктивно. Переменные каждой строки, имеющие значение логического 0, в конституенты входят с отрицанием (записываются в произведение в инвертированном виде), а переменные, имеющие значения логической 1 - без отрицания. Любую логическую (булеву) функцию можно представить дизъюнкцией конституент. Если одно из произведений не содержит хотя бы одной переменной, то такая форма называется нормальной дизъюнктивной формой (НДФ). Например:  Совершенная нормальная конъюнктивная форма (СНКФ). СНКФ можно построить по таблице истинности также как СНДФ. Для чего все значения функции представляют в инверсном виде и записывают СНДФ для инверсной функции. Далее, используя закон де Моргана, получают конъюнкцию всех дизъюнкций. В каждую дизъюнкцию входят все переменные строки таблицы, для которой функция до инвертирования принимала значение логической 1. Если (хотя бы одна) дизъюнкции, которые называются также макстермами (конституентами нуля), не содержат отдельные переменные, то такая форма записи функции называется нормальной конъюнктивной формой (НКФ). Пример записи СНКФ. Пусть функция представлена в виде таблицы истинности (рис. 1.9).

Элементарные функции алгебры-логики. Среди всех функций алгебры логики особое место занимают функции одной и двух переменных, называемые элементарными. В качестве логических операций над переменными, эти функции позволяют реализовать различные функции от любого числа переменных. Общее количество функций АЛ от m переменных R=2k, где k=2m. Рассмотрим элементарные функции от двух переменных

Полная система логических функций |

| 1.5. Полная система логических функций. Понятие о базисе

Функционально полная система логических функций представляет собой набор логических функций, с помощью которых можно записать любую, сколь угодно сложную функцию. В этом случае говорят, что этот набор образует базис. Функционально полными являются 3 базиса:

1) "И-ИЛИ-НЕ" (базис конъюнкции, дизъюнкции, инверсии) 2) "И-НЕ" (базис Шеффера) 3) "ИЛИ-НЕ" (базис Пирса или функция Вебба).

Примеры реализации логических операций в базисах “И-НЕ” и “ИЛИ-НЕ”.

Реализация операции “ИЛИ”: Пример реализации комбинационного устройства в базисе "И-НЕ". Пусть задана функция, реализуемая комбинационным устройством, в аналитической форме

Используя закон де Моргана и с учетом закона двойного инвертирования, запишем эту функцию в виде

Как следует из полученного аналитического выражения, логическое устройство должно содержать три двухвходовых и один трехвходовой элемент И-НЕ. Функциональная схема комбинационного устройства, построенная в базисе И-НЕ, показана на рис. 1.10.

|

Представление чисел в современных цифровых устройствах

имеют значения 1, 16, 256, 4096, и т.д.

Двоичная система счисления. Понятие весовых коэффициентов сохраняется и для чисел двоичной системы счисления (основание Р = 2). Рассмотрим пример, где число представлено в двоичной системе счисления и имеет вид 11011012 (индекс "2" в конце числа показывает, что число представлено в двоичной системе счисления). Десятичный эквивалент этого числа, т.е. значение числа в привычной для нас системе счисления, определим, используя весовые коэффициенты разрядов символов

11011012 =1·26 + 1·25 + 0·24 + 1·23 + 1·22 + 0·21 + 1·20 =

= 1·64 + 1·32 + 0·16 + 1·8 + 1·4 + 0·2 + 1·1 = 10910.

Таким образом, десятичный эквивалент двоичного числа определяется как сумма весовых коэффициентов разрядов, имеющих единичный сомножитель.

В цифровой технике часто используется и двоично-десятичная система счисления. При этом каждый разряд десятичного числа представляется четырьмя разрядами двоичного числа. Очевидно, что при этом используются не все значения четырехразрядного двоичного числа, т.к. оно может реализовать числа от 0 до 15, а в двоично-десятичной системе используется лишь значения от 0 до 9.

Арифметические основы цифровых устройств. При выполнении различных операций в современных цифровых устройствах и системах числа обычно представляются в двоичной системе счисления. Это связано с тем, что для представления смысла символов цифр двоичной системы счисления можно использовать простые электронные схемы с двумя электрическими состояниями. Принято, что символ “1” представляется некоторым стандартным уровнем напряжения или тока, а “0” - нулевым или близким к нулю уровнем напряжения или тока.

Арифметические операции над двоичными числами могут производиться по тем же правилам, что и над десятичными, однако, с целью упрощения цифровых систем для выполнения арифметических операций применяют алгоритмы, отличные от алгоритмов действий десятичной арифметики.

В двоичной системе счисления для представления знака числа используется дополнительный знаковый разряд (один или несколько разрядов), который располагается перед старшим числовым разрядом. Для положительных чисел значение знакового разряда Зн.р.=0, для отрицательного числа Зн.р.=1.

Операция вычитания в цифровых системах реализуется с помощью операции сложения. Вычитаемое при этом представляется в дополнительном коде (если расчет не требует высокой точности - в обратном коде).

Двоичный код со знаком называют также прямым кодом. В качестве примера рассмотрим положительное и отрицательное числа, десятичный эквивалент которых равен 4610.

|

Обратный код получается путем замены всех “0” на “1” и всех “1” на “0” прямого кода (двоичного числа со знаком). Причем, знаковый разряд при этом остается неизменным.

Замена “0” на единицу (“1”) называется инвертированием (также и замена “1” на “0”).

Обратный код, дополненный единицей в младшем разряде, называется дополнительным кодом. Последовательность действий при получении дополнительного кода:

Сложение и вычитание двоичных чисел. Правила сложения двух двоичных чисел можно показать на следующем примере:

Пример сложения многоразрядных чисел. Требуется сложить два числа 1810 и 2310

Вычитание в цифровых устройствах производится также как и сложение, только вычитающее представляется в дополнительном коде. Рассмотрим два примера, в первом требуется из числа 23 отнять число 18, а во втором из 18 отнять 23. С начала вычитающие представим в дополнительном коде

|

|

В результате полученное число соответствует числу минус пять (-5).

Принято считать, что дополнительный код положительного числа совпадает с его прямым кодом.

Операция вычитания с использованием только обратного кода (без дополнительных операций по переводу его в дополнительный код) приводит к ошибке, определяемой единицей в младшем разряде, и поэтому при точных расчетах не применяется.

|

1.2.

Представление чисел в современных цифровых устройствах Системы счисления. Система счисления - это код, в котором использованы специальные символы для обозначения количества каких либо объектов. Количество символов в системе счисления носит название его основания. Например, система счисления с основанием 10 имеет десять символов от 0 до 9. Система счисления с основанием два содержит всего два символа, эта система называется двоичной системой счисления. В шестнадцатеричной системе используется 16 символов и т.д. Чем меньше основание системы счисления, тем больше разрядов требуется для представления одного и того же количества объектов. Количественное значение символа определяется его номером разряда, т.е. местом расположения этого символа в числовом ряду. Десятичная система счисления. Основание этой системы счисления Р=10, так как для записи цифр разрядов используется десять символов. В качестве примера возьмем десятичное число 523.0. Здесь цифра 5 обозначает число 500, так как оно занимает по порядку 3-й разряд слева от десятичной точки. 523 = 5•102 + 2•101 + 3•100 - отсюда следует, что каждый разряд имеет свой “вес”. В зависимости от номера разряда (т.е. от номера позиции символов) разряды имеют следующие весовые коэффициенты  Таким образом, весовой коэффициент разряда в общем случае определяется как Рn-1, где n-порядковый номер разряда после точки (для целых чисел обычно точка не указывается, но подразумевается). Разряды справа после точки имеют следующие веса: Р-1, Р-2, и т.д. Шестнадцатеричная система счисления. Основание этой системы Р = 16 и для записи цифр разрядов используются 16 символов 0, 1, 2, . . . 9, А, В, С, D, Е, F. Весовые коэффициенты определяются как Рn-1, т.е. Вопросы и задания1.1. Какие виды сигналов используются в информационных системах? 1.2. Числа какой системы счисления используются в вычислительной технике? 1.3. Как связаны законы алгебры логики и работа элементов цифровой логики? 1.4. Как понять смысл “задания” функций АЛ? 1.5. Какие законы АЛ отражают суть понятий о базисе? 1.6. Нарисуйте схему цифрового логического замка в базисе И-НЕ, в которой сигнал на выходе замка принимает значение лог. “1” (Z= 1) при выполнении условия Х1=0; Х2=1; Х3=1; X4=1; X5=0 X6=1.

|

Анализ комбинационных устройств

| 2.10.

Анализ комбинационных устройств

Анализ - это процесс получения логического выражения для существующего комбинационного устройства, т.е. при анализе необходимо получить оптимальное логическое выражение (если требуется и СНДФ) имеющейся логической схемы. Необходимость в анализе КУ возникает при модернизации логических устройств, обновлении элементной базы, а также при оптимизации схемы цифрового автомата. Рассмотрим пример анализа простейшего логического устройства. Пусть дан фрагмент схемы комбинационного устройства, приведенный на рис. 2.31. Требуется минимизировать логическое выражение, реализуемое этой схемой и синтезировать новую схему в базисе “И-НЕ”. В начале анализа присваиваем имена промежуточным функциям на выходе каждого элемента и запишем логические выражения для этих функций Z1 =     Z4 = Z3 X1 = (    Выходная функция КУ представляет дизъюнкцию трех переменных (функций Z2, Z4 и Х4) с последующей инверсией Y =  Для удобства в преобразовании функцию Y представим в инверсном виде (а в конце процесса анализа снова вернём в исходный вид), тогда

Используя закон де Моргана, преобразуем инверсию конъюнкции

С учетом правил преобразования функцию Y приведем к виду

= Х4 +     Вернём функцию в исходную форму, т. е. снова проинвертируем Y =  Полученная функция соответствует минимальной форме и содержит всего одну конъюнкцию. Очевидно, в общем случае может получиться сложное логическое выражение, требующее минимизации с использованием известных методов, в частности карт Карно.

Рис. 2.31 Фрагмент схемы комбинационного устройства с указанием промежуточных функций Схема вновь построенного комбинационного устройства в базисе “И-НЕ” приведена на рис. 2.32. Из рис. 2.32 следует, что для реализации операции отрицания переменных Х3 и Х4 использованы элементы “И - НЕ” с объединенными входами. Такой же элемент использован для отрицания промежуточного результата функции после элемента “3И-НЕ”.

Рис. 2.32. Фрагмент схемы КУ, приведенный в базис И-НЕ Схема КУ, приведенная в единый элементный базис обладает большей устойчивостью, так как количество переменных сократилось (в результате упрощения “выпала” переменная Х1).

|

Дешифраторы

| 2.4.

Дешифраторы

Линейный или одноступенчатый дешифратор. Дешифратор - это комбинационное устройство, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. Обычно, указанный в схеме номер вывода дешифратора соответствует десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в качестве входных переменных, вернее сказать, что при подаче на вход устройства параллельного двоичного кода на выходе дешифратора появится сигнал на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода. Отсюда следует то, что в любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора. В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического 0 (при этом на всех остальных выходах уровень логической 1). В дешифраторах каждой выходной функции соответствует только один минтерм, а количество функций определяется количеством разрядов двоичного числа. Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором (в качестве примера неполного дешифратора можно привести дешифратор двоично-десятичных чисел). Рассмотрим пример синтеза дешифратора (полного) 3 ® 8, следовательно, количество разрядов двоичного числа - 3, количество выходов - 8. Таблица состояний дешифратора

7Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции (рис. 2.9). Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m)и m элементов отрицания. Пирамидальные дешифраторы. Пирамидальные дешифраторы позволяют реализовать схему на базе только двухвходовых элементов логического умножения (конъюнкции). Рассмотрим пример реализации дешифратора 3®8

Для построения такого дешифратора потребуется 12 двухвходовых элементов 2И и три инвертора. Пирамидальные дешифраторы при больших количествах входных переменных позволяют несколько упростить конструкцию устройства, т.е. уменьшить количество интегральных микросхем. Промышленностью стран СНГ, в том числе и России, выпускаются различные модификации дешифраторов в интегральном исполнении. Обозначение дешифраторов на принципиальных схемах показано на рис. 2.10.

Двухступенчатые дешифраторы на интегральных микросхемах. Пример дешифратора для пятиразрядного двоичного кода. Каждый дешифратор выполнен с управляющими входами, объединенными конъюнктивно. При выполнении условия конъюнкции на выходе, номер которого соответствует десятичному эквиваленту двоичного кода, появится уровень логического “0”. В противном случае все выходы находятся в состоянии логической единицы (рис.2.11). Как следует из рис. 2.11, пятиразрядный дешифратор, имеющий 32 выхода, выполнен на базе четырех дешифраторов с использованием лишь одного дополнительного инвертора, что достигнуто благодаря наличию входной управляющей логики каждой интегральной микросхемы. Нетрудно заметить, что входная логика дешифраторов КР1533ИД7 позволяет реализовать функцию дешифратора 2®3 без дополнительных элементов, а полного дешифратора 2®4 с использованием одного инвертора.

|

Гонки в комбинационных устройствах

е. безынерционные, ( что на практике достичь не удается), на выходе схемы КУ импульс помехи отсутствует. Однако в реальных схемах всегда имеет место явление гонок и требуется создать такие схемы, в которых влияние этого явления устраняется.

Борьба с гонками. Существует три наиболее часто встречающихся способа борьбы с гонками:

- тактирование;

- построение противогоночных схем;

|

- учет минимального времени задержки распространения сигнала. Пример реализации тактирования цикла работы комбинационного устройства (рис.2.4).

|

|

2.2.

Гонки в комбинационных устройствах Комбинационное устройство (КУ) - это устройство с m входами и n выходами. Если КУ выполнено на базе идеальных, т.е. безинерционных элементов, состояние выходов однозначно определяется состоянием входов в тот же момент времени. Однако, инерционность элементов и наличие различных факторов, приводящих к задержке распространения сигнала, приводят к задержке появления выходных сигналов КУ, т.е. сигналы на выходе КУ, соответствующие новому состоянию входных сигналов, появляются не сразу, а с некоторой задержкой. При этом в переходный период возможно появление на выходах устройства некоторых промежуточных значений сигналов, не соответствующих заданному состоянию устройства. Такое явление получило название состязаний или гонок. Обычно, вырабатываемые узлами КУ промежуточные значения сигналов, представляют собой импульсы очень малой длительности, являющиеся помехой для всей цифровой системы. Они могут запускать непредусмотренное срабатывание триггеров, счетчиков и осуществлять нежелательные записи в регистры. Рассмотрим в качестве примера фрагмент схемы комбинационного устройства (рис. 2.1), где может наблюдаться явление гонок. Для наглядности процесса формирования промежуточного значения выходного сигнала приведены временные диаграммы состояний различных цепей распространения в идеальном и реальном случаях (рис.2.2, рис. 2.3).

Время задержки импульсов в цепях определяется средним временем задержки распространения сигнала всеми элементами этой цепи. Момент времени появления импульса помехи определяется соотношением числа инвертирующих элементов в конкурирующих цепях фрагмента схемы КУ (см. рис.2.2, а и рис.2.3). Как следует из рис.2.2, а, если элементы схемы идеальные, т. Многоразрядный сумматор с последовательным

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис. 2.23 приведена схема, предназначенная для сложения двух четырехразрядных чисел А и В. Эта схема выпускается в интегральном исполнении. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивания разрядности схемы.

Рис. 2.23. Сумматор с последовательным переносом

Мультиплексоры |

Если Х1=Х2=0, на выход мультиплексора будет передаваться сигнал с входа D0. Когда на адресных (управляющих) входах Х1=1 и Х2=0, то на выход будет передаваться сигнал с входа D1 и т.д.

Мультиплексоры нашли широкое применение в вычислительной технике в качестве коммутаторов цифровых сигналов. Они используются в компьютерах и микропроцессорных контроллерах для коммутации адресных входов динамических оперативных запоминающих устройств, в узлах объединения или разветвления шин и т.д. На базе мультиплексоров можно построить различные комбинационные устройства с минимальным числом дополнительных элементов логики. Следует отметить, что мультиплексоры хотя, и предназначены для коммутации цифровых сигналов, но с помощью мультиплексоров, изготовленных по КМОП технологии, можно коммутировать и аналоговые сигналы.

Универсальные логические модули (УЛМ) на МS. Кроме ком-мутационных функций, мультиплексоры позволяют реализовать комбинационные устройства на m (m-количество управляющих входов) входов и на один выход. Если комбинационное устройство, построенное на базе мультиплексора, не требует подключения дополнительных элементов логики, оно называется универсальным логическим модулем. Отметим, что мультиплексор 8 ®1 (3 управляющих и 8 информационных входов) позволяет реализовать любую функцию трёх переменных.

Для получения УЛМ управляющие входы мультиплексора представляют как информационные, а информационные входы - как настроечные (следовательно, у мультиплексора 8 ®1 будут три информационных и 8- настроечных входов).

Пусть функция задана в виде карты Карно (рис.2.15).

|

При построении УЛМ на карте Карно минимизационные контуры не проводятся.

По карте записывается СHДФ с учетом состояния информационных (настроечных) входов мультиплексора.

Cопоставляя полученную СHДФ с формулой мультиплексора, определяем номера коэффициентов “а”, т.е.

Следовательно, эти коэффициенты равны единице, т.е. D0 = D3 = D5= D6 = 1, а на остальных настроечных входах логические нули, т.е. D1 = D2 = D4 = D7 = 0.

Схема комбинационного устройства, построенного на базе мультиплексора 8-1 и реализующего функцию f (x), приведена на рис. 2.16.

Как следует из рис. 2.16, построение комбинационного устройства на базе мультиплексора сводится к объединению настроечных входов так, чтобы получилось две группы. К одной группе входов, в соответствии с заданной функцией, подают логический “0”, а другой - “1”.

|

На базе мультиплексоров можно синтезировать комбинационные устройства, которые могут реализовать функции на большее число переменных, чем количество управляющих входов мультиплексора. Очевидно, и в этом случае, мультиплексор сохраняет свою универсальность, так как часть переменных реализуемой функции непосредственно подается на входы Х1 . . . Хm мультиплексора (количество переменных, непосредственно подаваемых на управляющие входы мультиплексора равно m).

Синтез комбинационного устройства на мультиплексоре, реализующего функцию с числом переменных больше, чем число управляющих входов мультиплексора. Часто использование мультиплексора при синтезе КУ существенно упрощает этот процесс и схему цифрового автомата.

В общем случае, когда требуется синтезировать КУ, реализующее функцию N аргументов на мультиплексоре с M управляющими входами и 2М информационными входами, М младших переменных из набора Х1, Х2, . . . .

ХN следует подать на управляющие входы, а информационные сигналы (настроечные) D0, D1, . . . . D2м нужно представить функциями остальных (N - M) переменных, как показано на рис. 2.17. Тогда синтез КУ сводится, по сути дела, к синтезу схемы формирования информационных сигналов, которую можно рассматривать как внутреннее более простое КУ.

|

Рассмотрим пример синтеза КУ для реализации функции пяти переменных на мультиплексоре с двумя управляющими входами. Тогда “младшие” переменные Х1 и Х2 подаются на управляющие входы Х1и Х2, соответственно. Выходную функцию Y будет определять карта Карно управления информационными входами (рис. 2.18). Каждый информационный сигнал, в свою очередь, является функцией трех переменных: Х3, Х4, Х5. Для каждого информационного сигнала можно составить карту Карно и с её помощью минимизировать логическое выражение функций D0, D1, D2 и D3. По минимизированным логическим выражениям строится схема формирования информационных сигналов (настройки) в любом известном базисе.

На мультиплексорах с двумя управляющими входами легко можно синтезировать КУ при числе переменных N £ 6. На мультиплексорах с тремя и четырьмя управляющими входами можно синтезировать функции и большего количества переменных. Карты управления информационными входами для этих случаев показаны на рис. 2.18.

При синтезе КУ на мультиплексорах можно использовать следующий алгоритм действий:

-составить таблицу истинности КУ;

-подать на управляющие входы мультиплексора младшие переменные;

-представить информационные сигналы функциями остальных переменных и составить карту Карно для каждого информационного сигнала;

- минимизировать логические выражения для сигнала на каждом информационном входе;

- по логическим выражениям составить схему формирования сигналов, подаваемых на информационные входы мультиплексора.

В задачу синтеза комбинационных устройств

|

2.1.

Основные этапы синтеза комбинационных устройств В задачу синтеза комбинационных устройств входит построение схемы устройства по заданным условиям его работы и при заданном базисе элементов. Задание комбинационного устройства сводится к заданию тех функций, которые оно должно реализовать. Число функций определяется числом выходов комбинационного устройства. Процесс синтеза комбинационных устройств состоит из 2-х этапов. 1. Абстрактный синтез Абстрактный синтез включает: формирование задачи, словесное описание функций устройства, определение типа устройства; описание устройства на формализованных языках: таблица истинности, карта Карно, аналитическое выражение и т.д.; минимизация булевых функций; построение логической схемы устройства. 2. Схемный синтез переход в требуемый базис; построение принципиальной схемы; разработка монтажной схемы; изготовление устройства и его испытания. В результате испытаний осуществляются корректировка схемы и подготовка технической документации. |

Программируемые логические матричные структуры

| 2.9.

Программируемые логические матричные структуры

Реализация Булевых функций с помощью матричных схем. Матричные схемы представляют собой сетку ортогональных проводников, на местах пересечения которых установлены элементы односторонней проводимости (ЭОП) (диоды, транзисторы). Матричные схемы бывают 2-х и 3-х уровневые. Каждый уровень называется матрицей. Матрица первого уровня называется матрицей М1, матрица второго уровня - М2. Обычно матрица М1 реализует элементарные конъюнкции и называется матрицей конъюнкций, а матрица М2 - матрицей дизъюнкций, т.к. позволяет реализовать дизъюнкции переменных. Рассмотрим двухуровневую матричную схему (рис. 2.26).

Рис. 2.26. Функциональная схема матрицы М1:S=3;q=4 Количество входов матрицы М1 равно S, т.е. Х1, Х2, . .. , Xs, количество выходов матрицы М2 равно t, т.е. Y1, Y2, . . , Yt. Буквой Р обозначаются промежуточные проводники, перпендикулярные (ортогональные) проводникам Х и У. Количество ортогональных проводников равно q. Функциональная схема матрицы М1 представлена на рис. 2.27. Рассматриваемая матрица может реализовать четыре конъюнкции, по числу ортогональных проводников: Р1 = Х3 Х2     В общем случае, если какие-либо ортогональные проводники не участвуют в реализации конъюнкций, их число может быть меньше q.

Рис. 2.27. Функциональная схема матрицы М1:S=3;q=4 Реализация необходимых конъюнкций осуществляется путем прожига перемычек (включенных последовательно с полупроводниковым диодом), расположенных на местах пересечения ортогональных проводников, не участвующих в образовании конъюнкций. Следует отметить, что в исходном состоянии на всех пересечениях проводников матрицы М1 имеются соединения, т.е. матрица реализует все конъюнкции переменных, причем в каждую конъюнкцию входят все переменные и с отрицанием, и без. Очевидно, что такие конъюнкции логического смысла не имеют. Для получения необходимых конъюнкций следует прожигать все легкоплавкие перемычки, находящиеся на узлах, не участвующих в конъюнкциях. На схеме (рис. 2.27) рассматриваемой матрицы М1 крестиками обозначены узлы, на которых сохранены перемычки. Рассмотрим процесс реализации конъюнкции на примере P1 = Х3Х2  Схема матрицы дизъюнкции М2 содержит сопротивления нагрузки и транзисторные ключевые соединители (на местах пересечений ортогональных проводников). На рис. 2.28 приведена схема матрицы М2 для двух выходов ( количество проводников Р одинаково для М1 и М2 и в данном примере q = 4).

Рис. 2.28. Матрица дизъюнкций М2 Матрица М2, приведенная на рис.1, реализует две дизъюнкции:

Объем информации, который можно записать в матричную схему, определяется как информационная площадь матриц, вернее суммой Sm1 и Sm2. Sm = Sm1 +Sm2 = 2Sq + qt. На практике часто встречаются схемы, состоящие из матриц М2 и дешифратора (полного). Такие схемы обычно называют постоянными запоминающими устройствами (ПЗУ). ПЗУ - это элемент (устройство) памяти, позволяющий хранить записанную в нем информацию, и после выключения напряжения источника питания. По способу записи ПЗУ подразделяются на масочные, программируемые и репрограммируемые. Масочные ПЗУ программируются заводом изготовителем с помощью специальных масок, т.е. соединения на местах пересечения ортогональных проводников заложены в технологию производства ПЗУ. Программируемые ПЗУ (ППЗУ). ППЗУ выпускаются заводом-изготовителем в "чистом виде", т.е. по всем адресам записаны"0". Программирование ППЗУ осуществляется пользователем ППЗУ на специальной установке, называемой программатором. В ППЗУ можно записать (его программировать) информацию только один раз. Изменить записанную информацию или исправить ее нельзя. ППЗУ нашли широкое применение в ЭВМ для хранения запускающих программ. Они обладают большим быстродействием, чем репрограммируемые ПЗУ (РПЗУ). Репрограммируемые ПЗУ позволяют, при необходимости, перепрограммировать ПЗУ, т.е. стереть ранее записанную информацию и записать новую. По способу стирания ранее записанной информации РПЗУ бывают с ультрафиолетовым (ультрафиолетовыми лучами) и электрическим стиранием. РПЗУ позволяют десятки (некоторые до 1000) раз перепрограммировать и сохранять записанную информацию десятки и сотни тысяч часов. Быстродействие РПЗУ несколько хуже быстродействия ППЗУ. Независимо от типа и способа стирания ПЗУ имеют структуру, приведенную на рис. 2.29.

Рис.2.29. Структурная схема постоянного запоминающего устройства Структурная схема ПЗУ содержит дешифратор на S входов и 2S -выходов, а также матрицу М2. Информационная емкость ПЗУ определяется как Sпзу = 2S, где S- количество входов X. В этом определении емкости (объема) памяти не учтено количество выходов Y(t). Обычно число t бывает 4, 8, и 16 (полубайтовая, байтовая и двухбайтовая организация памяти). "Битовая" емкость ПЗУ определяется как Sпзу (бит) = 2S t (бит). Промышленностью выпускаются ПЗУ с объемом памяти (информационной емкостью) на 2 кбайт, 4 кбайт,16 кбайт,32 кбайт и т.д., где к=1024; 1байт=8бит.

Рис. 2.30. Схемное обозначение РПЗУ К573РФ2, К573РФ5 с ультрафиолетовым стиранием: А - адресные входы; D – информационные выходы. Uce – вход подачи напряжения записи (в режиме хранения на этот вход подается Ucc); Ucc – вывод для подачи напряжения питания. СЕ и ОЕ –входы управления состоянием выводов, если СЕ=ОЕ=1, входы D имеют высокоимпедансное состояние. При СЕ=ОЕ=0 вывод информации разрешен. Микросхема РПЗУ К573РФ2 (РФ5) имеет одиннадцатиразрядный дешифратор, выходы которого соединены с восьмиразрядной матрицей М2. В процессе записи выходные элементы РПЗУ находятся в режиме приема информации через выводы D0 . . . D7 (на входе “ОЕ“ уровень “1”). В режиме считывания записанной информации выводы “Uce” и “Ucc” объединяются, и на них подается напряжение питания +5В.

|

Схема полусумматора.

Сумматор. В отличие от полусумматора должен воспринимать 3 входных сигнала: 2 слагаемых и сигнал переноса с предыдущего разряда.

Сумматором называется операционный узел ЭВМ, выполняющий операцию арифметического сложения двух чисел.

Чтобы понять сущность работы комбинационного сумматора, рассмотрим примеры суммирования двух одноразрядных двоичных чисел:

Из приведенных примеров (1 - 4) видно, что если отсутствует перенос из младшего разряда, то перенос в старший разряд может быть только в одном случае, когда оба числа равны единице. Если же имеется перенос из младшего разряда, то перенос в старший разряд будет всегда, кроме одного случая, когда оба слагаемых равны нулю.

Составим таблицу функционирования:

| ai | bi | Сi | Si | Сi+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Схема сумматора может быть реализована на двух полусумматорах, соединенных как указано на схеме рис. 2.22. В этой схеме выделим промежуточные сигналы Pi, gi, ri. Введем эти сигналы в новую таблицу функционирования. Соответствие работы этой схемы (рис. 2.22) и таблицы фунционирования можно проверить перебором всех возможных вариантов.

Рис. 2.22. Схема полного сумматора

это логическое устройство, выполняющее преобразование

|

2.5.

Шифраторы Шифратор - это логическое устройство, выполняющее преобразование позиционного кода в n разрядный двоичный код. Таким образом, шифратор - это комбинационное устройство, реализующее обратную дешифратору функцию. Пример шифратора для трех переменных. Таблица состояния шифратора:

Схема шифратора семиразрядного позиционного кода в трехразрядный двоичный код приведена на рис. 2.12.

|

Синтез комбинационного устройства-преобразователя кода

| 2.3. Синтез комбинационного устройства-преобразователя кода

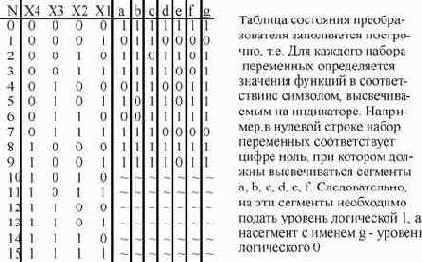

нормам. В данном случае будем считать, что сегменты будут высвечиваться при подаче на них уровня логической “1”.

Для зажигания цифры 1 необходимо подать уровни логической “1” на сегменты “b” и “c” и т.д. Преобразователь предназначен для индикации цифр десятичной системы счисления, и поэтому значения функций для наборов переменных, начиная с номера 10, для индикатора безразличны. Безразличные значения функций обозначены знаком ~ (тильда). После заполнения таблицы состояния устройства составляются аналитические выражения (СНДФ) для каждой функции и строятся карты Карно, предназначенные для минимизации этих функций. Карты Карно можно заполнять и без записи СНДФ, что сократит количество действий разработчика при синтезе устройства. Очевидно, что без минимизации функции преобразователя получились бы весьма громоздкими, т.к. каждая содержала бы по девять минтермов, состоящих из четырех переменных. Порядок составления карт Карно и получения минимальных НДФ роли не играют. Для удобства с точки зрения последовательности изложения алгоритма действий, минимизацию начнем с функции а (рис.2.6), реализующей индикацию цифры 0.

Для функции b карта Карно представлена на рис.2.7. Она содержит три контура, следовательно, МДФ будет содержать всего три простых конъюнкции.

Карта Карно для функции “c” представлена на рис.2.8. Она содержит четыре контура, следовательно, функция будет содержать тоже четыре минтерма.

Аналогично строятся карты Карно и записываются минимальные ДФ и для других функций. После получения всех МДФ производят выбор требуемого базиса логических элементов и составляют принципиальную схему. Многие фрагменты отдельных функций могут быть использованы при реализации общих для этих функций операций. В общем случае, принципиальную схему преобразователя кода можно построить на базе элементов И-ИЛИ-НЕ.

|

это логическая цепь, которая вырабатывает

|

2.8.

Синтез комбинационных сумматоров Полусумматор это логическая цепь, которая вырабатывает сигналы суммы (S) и переноса (С) при сложении двух двоичных чисел а и в. Составим таблицу функционирования.

Эти выражения упрощению не поддаются. Приведем к виду, удобному для реализации на элементах ИЛИ-НЕ.   исходя из полученных формул составим схему полусумматора (рис. 2.20, а):  Рис.2.20. Схема полусумматора Поскольку полусумматор имеет широкое применение и его выпускают в виде отдельной микросхемы, он имеет собственное обозначение (рис. 2.20 б). Составляя дизъюнктивную нормальную форму для полусумматора, мы получили следующие булевы функции:   Следовательно, перенос происходит с помощью функции И, а выработка сигнала суммы (функции неравнозначности) производится элементом ИСКЛЮЧАЮЩЕЕ – ИЛИ. На рис.2.21 показана схема полусумматора, составленная из этих элементов.  Составим логическую цепь трехвходовой пороговой | ||||||||||||||||||||||||||||||||||||||||||||||||

|

Сумматоры с параллельным переносом

Чтобы уменьшить время операции сложения многоразрядных чисел можно использовать схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных.

Согласно таблице переключений, в общем случае для сигнала переноса любого i-го разряда справедливо соотношение:

Величины gi, ri вычисляются в качестве промежуточных результатов и в полном сумматоре. Следовательно, их получение не требует дополнительных затрат. Смысл этих величин объясняется совсем просто. Сигнал gi вырабатывается тогда, когда в данном разряде перенос происходит из-за комбинации входных переменных ai,bi. Поэтому его называют функцией генерации переноса. Сигнал Pi показывает, передается ли полученный в младшем разряде сигнал переноса Ci дальше. Поэтому он называется функцией распространения переноса.

Пользуясь выражением (1), можно вывести следующие формулы для вычисления сигналов переноса:

Очевидно, что хотя полученные выражения достаточно сложные, время формирования сигнала переноса в любой разрад с помощью вспомогательных функций определяется только времением здержки распространения сигнала на двух элементах. Эти функции реализуются специальным комбинационным устройством – схемой ускоренного переноса.

Схема сумматора с параллельным переносом приведена на рис. 2.24, а. На рис. 2.24, б изображена схема устройства параллельного переноса в группе из четырех разрядов. Эта схема реализует систему уравнений (2).

Рис. 2.24. Схема сумматора с параллельным переносом

Синтезируйте схему преобразователя кода для

2.1. Объясните причины возникновения гонок в комбинационных устройствах.

2.2. Синтезируйте схему преобразователя кода для 9 и 13 сегментных индикаторов.

2.3. Можно ли построить полный дешифратор на элементах базиса ИЛИ-НЕ? Составьте аналитическое выражение (функции), описывающее работу дешифратора в базисе И-НЕ.

2.4. Синтезируйте схему мультиплексора 2-1, и на базе синтезированного мультиплексора постройте схему сумматора по модулю два (исключительное ИЛИ).

2.5. Определите информационную площадь (SПЛМ) ПЛМ, ПЗУ при произвольных значениях количества информационных входов. Докажите, что SПЗУ > SПЛМ.

2.6. Нарисуйте схему фрагмента КУ, приведенного на рис. 2.32, в базисе ИЛИ-НЕ.

2.7. Нарисуйте схему четырёхразрядного полного дешифратора на базе дешифраторов 2-4. Базовые дешифраторы имеют один дополнительный вход стробирования.

D-триггер

В технической литературе D-триггер, управляемый уровнем синхроимпульса, известен также как триггер-защелка.

Пример синтеза D-триггера, управляемого уровнем синхроимпульса из асинхронного одноступенчатого RS-триггера. Для этого D-триггер представляют как совокупность RS-триггера и комбинационного входного устройства, т.е. представляется так, что входными линиями RS-триггера управляет комбинационное устройство (КУ), согласно характеристической формуле D-триггера (см. рис. 3.11, в). Входными переменными КУ являются сигналы Q0 , C, D, а выходными (функциями) - S и R. Если учесть, что сигналы R и S являются для RS-триггера управляющими сигналами, то таблица состояний синтезируемого триггера будет содержать пять столбцов: два столбца - для переменных D-триггера - D и Q0, один - для функции Q (выходной сигнал синтезируемого триггера, он же является выходным сигналом базового RS-триггера) и два столбца - для переменных R и S RS-триггера

|

Из таблицы (рис.3.12, а, первая строка) следует: если триггер находился в состоянии “0” (Q0 =0), чтобы он сохранил это состояние и после поступления очередного синхроимпульса (отметим, что переключение состояния триггера происходит только при наличии синхроимпульса, а каждая строка таблицы состояний соответствует новому синхроимпульсу) на входе S (RS-триггера) необходимо поддерживать уровень “0”, а на входе R - любой уровень, т.к. когда триггер находится в состоянии”0”, он сохраняет это состояние независимо от состояния сигнала R.

Для второй строки таблицы состояний Q0=1, а новое состояние триггера “0” (Q=0), следовательно, необходимо подать на вход R - уровень логической 1 и т.д.

Для каждой строки, где Q0=1, это состояние триггера сохранится независимо от значения сигнала S (т.к. при S=0 - режим хранения, а при S=1 - запись единицы).

После заполнения таблицы состояний, используя карты Карно (рис. 3.12, б и в), записывают логические выражения для функций комбинационного устройства S и R (следует помнить, что эти сигналы являются функциями аргументов Q0 , D и входными переменными для RS-триггера.

По полученным логическим выражениям (см. рис. 3.12, б и в) можно построить схему D-триггера (рис. 3.12, г).

Рассмотренный выше D-триггер синтезирован на базе синхронного RS-триггера. Его можно синтезировать и на базе двухступенчатого, а также - простого, асинхронного RS-триггера. Как уже было отмечено выше, переключение D-триггера происходит только при наличии (поступлении) синхроимпульса. С учетом этого, логические функции S и R можно записать в виде

S = C D;

Схема, реализующая эти функции, содержит два элемента конъюнкции и один инвертор. На рис. 3.13 приведена схема D-триггера, построенного на базе асинхронного RS-триггера.

|

На рис. 3.14 приведено обозначение D-триггера К1533ТМ2, выпускаемого промышленностью в виде интегральной микросхемы (ИМС).

Обычно, в одном корпусе ИМС содержится два D-триггера, управляемых фронтом. D-триггеры в интегральном исполнении имеют также дополнительные асинхронные входы управления S и R. Функции асинхронных входов не зависят от сигналов синхронизации. Отметим, что асинхронные входы имеют и другие типы триггеров. Поскольку дополнительные входы “предустановка” и “очистка”, с помощью которых триггер может быть установлен в нужное состояние независимо от сигналов на других входах, включая синхронизирующий, работают независимо от синхронизации, их называют асинхронными.

Входы “предустановки” и “очистки” напоминают соответствующие входы S и R обычного несинхронизируемого RS-триггера. При подаче “1” на вход R и “0” на вход S (рис. 3.14) триггер устанавливается в состояние “0”. При подаче “1” на оба эти входа поведение триггера не определено, т.е. комбинация S=1, R=1 является запрещенной. При подаче на эти входы “1” поведение триггера полностью определяется другими входными сигналами и синхросигналом.

Функциональный счетчик В.М. Сапельникова

На этих триггерах собран девятиразрядный резистор сдвига. RS – триггер (элемент 10) применяется для задания режима работы функционального счетчика. С этой же целью используются еще два элемента 3И-НЕ (элементы 11 и 12). Синхронизирующие импульсы поступают от кнопки “СИ” (синхроимпульсы), и для устранения возможного “дребезга” применяются логические схемы 2И-НЕ (элементы 13-14).

Функциональный счетчик позволяет получать различные кодовые последовательности. Линейно - нарастающую кодовую последовательность получаем, когда триггеры регистра сдвига 1-9 последовательно от первого к последнему устанавливаются в состоянии “1”, а затем все одновременно устанавливаются в состояние “0”. Линейно убывающую кодовую последовательность, когда триггеры регистра сдвига последовательно от последнего к первому устанавливаются в состояние “0”, а затем все одновременно устанавливаются в состояние “1”.

Можно получить линейно-нарастающе-убывающую кодовую последовательность. Именно этой кодовой последовательности соответствует основной режим работы, используемый в калибраторе фазы и описываемый таблицей переключений (табл. 3.3).

Рассмотрим этот режим работы. В исходном состоянии триггеры 1-9 находятся в состоянии “0”, триггер 10 в состоянии “1”. На третьи входы элементов ЗИ-НЕ (элементы 11-12) устанавливается логический “0” переключателями S1 и S2. При этом на асинхронные R и S входы триггеров регистра сдвига поступает “1”.

Первый синхронизирующий импульс устанавливает триггер 1 в состояние “1”, не изменяя состояния других триггеров. После этого второй JK – триггер регистра сдвига подготовлен к записи “1” по третьему J–входу. Второй синхронизирующий импульс устанавливает триггер 2 в состояние «1» и по третьему J-входу подготавливает следующий триггер к приему “1”. Аналогично с приходом каждого последующего синхроимпульса и в соответствии с табл. 3.3 происходит переключение в “1” триггеров регистра сдвига до прихода девятого импульса. С приходом девятого синхроимпульса последний JK- триггер регистра сдвига переходит в “1”.При этом RS- триггер (элемент 10) переходит в состояние “0”. Переход RS-триггера в состояние “0” подготавливает все триггеры регистра сдвига к приему “0”. Так у девятого JK–триггера на два J-входа теперь поступает “0”, и на все три К - входа поступает “1” с выходов вспомогательного RS-триггера. Таким образом, последний JK-триггер готов к приему “0”. Остальные же восемь JK-триггеров будут последовательно готовиться к приему «0» путем подачи на первые К - входы недостающей “1” при переходе в состояние “0” находящегося справа от него JK-триггера. В этом случае на инверсном выходе JK-триггера появляется логическая “1”.

3.8. Функциональный счетчик В.М. Сапельникова Рис. 3.43. Управление таким ЦАП удобно производить с помощью функционального счетчика который должен иметь девять разрядов Q1 и таблицу переключений (табл. 3.3), определяющую код работы функционального счетчика. Цикл работы составляет 18 тактов и требует 18 синхроимпульсов С. Схема функционального счетчика приведена на рис. 3.44. Счетчик собран на девяти JK – триггерах (элементы 1 - 9) типа К155ТВ1, имеющих по три J – входа и три К – входа, объединенных по И. Триггеры имеют асинхронные установочные R и S входы. Электронные счетчики и делители частоты |

| 3.7. Электронные счетчики и делители частоты

На базе счетных триггеров можно построить цифровое устройство, получившее название электронного счетчика. Электронные счетчики ( далее, просто счетчики) позволяют вести подсчет электрических импульсов, количество которых (поступивших на вход счетчика) представляется, обычно, в параллельном коде. Счетчики могут отличаться модулем счета и типом счетной последовательности, которая, в частности, может быть двоичной, двоично-десятичной, в коде Грея и т.п. Цифровые последовательностные устройства, выполненные по схеме счетчика, но имеющие один счетный вход и один выход называются делителями частоты. Таким образом, любой счетчик может служить в качестве делителя частоты, если используется информация только одного из его выходов. Так как счетчики и делители имеют единую структуру, основное внимание будет уделено синтезу счетчиков. Счетчики и делители подразделяются на асинхронные и синхронные. У синхронных счетчиков все разрядные триггеры синхронизируются параллельно одними и теми же синхроимпульсами, поступающими из источника этих импульсов. Асинхронные счетчики имеют последовательную синхронизацию, т.е. каждый последующий разрядный триггер синхронизируется выходными импульсами триггера предыдущего разряда. Асинхронные счетчики иногда называют последовательными, а синхронные счетчики - параллельными. Синхронные счетчики, в свою очередь, подразделяются на параллельно-синхронные и последовательно-синхронные. Параллельные счетчики имеют более высокую скорость счета, чем асинхронные. Счетчики, независимо от способа синхронизации, подразделяются на счетчики прямого счета (суммирующие) и на счетчики обратного счета (вычитающие). В интегральном исполнении выпускаются также реверсивные счетчики, в которых имеется специальный вход для переключения режима работы, т.е. направления счета. Многие типы счетчиков, выпускаемые промышленностью в интегральном исполнении, имеют дополнительные входы предустановки, позволяющие использовать эти счетчики в режиме регистра памяти.  Рис. 3.33. Схема а), таблица состояний триггеров б) и временные диаграммы, поясняющие работу в) последовательного четырехразрядного счетчика на JK - триггерах Временные диаграммы, поясняющие работу асинхронного суммирующего счетчика приведены на рис. 3.33, в. Счетчики обратного счета (вычитающие счетчики). На рис. 3.34 приведена схема асинхронного трехразрядного двоичного вычитающего счетчика, построенного на базе D-триггеров. Отметим, что условия для изменения состояний триггеров вычитающих счетчиков аналогичны условиям для суммирующих счетчиков с той лишь разницей, что они должны “опираться” на значения инверсных, а не прямых выходов триггеров. Следовательно, рассмотренный выше счетчик можно превратить в вычитающий, просто переключив входы “С” триггеров с выходов Q на выходы  Работа вычитающего счетчика на D-триггерах наглядно иллюстрирована на рис. 3.34, (б). Из рис. 3.34 следует, что после нулевого состояния всех триггеров, с приходом первого синхроимпульса они устанавливаются в состояние “1”. Поступление второго синхроимпульса приводит к уменьшению этого числа на одну единицу и т.д. После поступления восьмого импульса, снова, все триггеры обнуляются и цикл счета повторяется, что соответствует модулю М=8.  В некоторых случаях необходимо, чтобы счетчик мог работать как в прямом, так и в обратном направлении счета. Такие счетчики называются реверсивными. Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Так, например, асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода пре-дыдущего JK- или Т-триггера на счетный вход последующего. В случае, когда реверсивный счетчик строится на базе D-триггеров, управляемых передним фронтом, для получения режима прямого счета следует соединить инверсный выход предыдущего с счетным входом последующего триггера. Все рассмотренные типы счетчиков могут быть использованы в цифровых устройствах “умеренного” быстродействия, когда частота следования синхроимпульсов не превышает критического значения, при котором время задержки установки триггеров последних (старших) разрядов счетчика становится соизмеримым с длительностью периода входных тактовых импульсов. В связи с этим, асинхронные счетчики строятся на относительно небольшое количество разрядов, так как при большем количестве разрядов выходные сигналы триггеров старших разрядов появляются позднее, чем управляющие фронты синхроимпульсов (поступающих на вход первого триггера) . Параллельные счетчики (синхронные счетчики). Как было уже сказано выше, параллельные счетчики бывают двух типов: синхронные параллельные и синхронные последовательные.  Синхронный последовательный счетчик. По способу подачи синхроимпульсов такие счетчики параллельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно, а по способу управления (подачи управляющих импульсов) - последовательные. Схема синхронного последовательного счетчика, реализованного на JK-триг-герах, приведена на рис. 3.35. Синхронный последовательный счетчик обладает повышенным быстродействием, однако, за счет последовательного формирования управляющих уровней, на входы “J” и “К” счетных триггеров, быстродействие несколько уменьшается. От этого недостатка лишены параллельные синхронные счетчики, в которых формирование управляющих уровней и их подача на соответствующие входы триггеров счетчика осуществляется одновременно, т.е. параллельно. Пример реализации параллельного синхронного счетчика иллюстрирован на рис. 3.36.  Поскольку счетчик имеет одну общую линию синхронизации, состояние триггеров меняется синхронно, т.е. те триггеры, которые по синхроимпульсу должны изменить свое состояние, делают это одновременно, что существенно повышает быстродействие синхронных счетчиков. Счетчики с произвольным коэффициентом счета. Принцип построения подобного класса счетных устройств состоит в исключении нескольких состояний обычного двоичного счетчика, являющихся избыточными для счетчиков с коэффициентом пересчета, отличающимися от двоичных. При этом избыточные состояния исключаются с помощью обратных связей внутри счетчика. Число избыточных состояний для любого счетчика определяется из следующего выражения: М = 2m - Ксч, где М - число запрещенных состояний, Ксч - требуемый коэффициент счета; 2m - число устойчивых состояний двоичного счетчика. Задача синтеза счетчика с произвольным коэффициентом счета заключается в определении необходимых обратных связей и минимизации их числа. Требуемое количество триггеров определяется из выражения n= [log2 Ксч], где [log2 Ксч] - двоичный логарифм заданного коэффициента пересчета Ксч, округленный до ближайшего целого числа. В каждом отдельном случае приходится применять какие-то конкретные методы получения требуемого коэффициента пересчета. Существует несколько методов получения счетчиков с заданным коэффициентом пересчета Ксч. Один их этих методов заключается в немедленном сбросе в “0” счетчика, установившегося в комбинацию, соответствующему числу Ксч. Его называют также методом автосброса. Рассмотрим пример реализации счетчика с Ксч=10 методом автосброса. Очевидно, что “сбрасывая” двоичный четырехразрядный счетчик на нуль каждый раз, когда он будет принимать состояние 1010, можно обеспечить”возврат” счетчика в исходное состояние после каждых десяти импульсов. Подобный прием удобно применять при использовании счетчиков в интегральном исполнении, имеющих ячейки конъюнкции (И) на входах установки в нуль, как это сделано в микросхеме К1533ИЕ5. В данном примере (рис. 3.37) организованы соединения, обеспечивающие коэффициент пересчета Ксч =10.

Как следует из рис. 3.37, роль ячейки, выявляющей факт достижения кодовой комбинации 1010 на выходах счетчика, играет ячейка И, уже имеющаяся на входе сброса ИМС К1533ИЕ5. В таблице 3.1 поясняются конфигурации соединений для получения различных коэффициентов пересчета с помощью счетчика К1533ИЕ5. Наиболее очевидные варианты получения коэффициентов (2, 4, 8, 16 ) в таблице не указаны. В графе “Соединения” таблицы указано, какие выводы микросхемы должны быть соединены между собой: например, указание 1-12 означает, что нужно соединить вывод 1 с выводом 12. В строках “Ввод” и “Выход” таблицы указаны номера выводов микросхемы, на которые следует подавать входные импульсы и с которых надлежит снимать выходные, соответственно. Следует отметить, что ИМС К1533ИЕ5 состоит из четырех счетных триггеров, один из которых имеет раздельные выводы входа и выхода, а остальные три триггера соединены последовательно по схеме асинхронного счетчика. Синтез счетчика с произвольным коэффициентом счета. Один из методов проектирования счетчиков с заданным коэффициентом счета заключается в построении таблицы переходов, в первых столбцах которых будут отражены текущие состояния триггеров счетчика, а в последующих - следующие за ними состояния. Анализ таблицы позволяет установить те переходы, которые должны быть “сделаны” триггерами, входящими в состав счетчика. Затем с помощью управляющей таблицы соответствующего триггера находятся значения логических функций на управляющих входах триггеров, позволяющие осуществить эти переходы. Рассмотрим пример синтеза синхронного двоично-десятичного счетчика на базе JK-триггеров. На рис. 3.38 показан граф, поясняющий последовательность переходов десятичного счетчика, в таблице 3.2 - таблица переходов.  В правой части таблицы 3.2 приведены значения входных сигналов четырех триггеров. Для поиска этих значений должны быть проанализированы реализованные переходы, а затем с помощью управляющей таблицы (см. рис. 3.15, а) определены соответствующие значения “J” и “K” входов триггеров.   На рис.3. 39 приведены карты Карно для логических функций, которым должны соответствовать сигналы, присутствующие на управ-ляющих входах триггеров ( нулевые значения функций в клетки карты Карно не записаны). После упрощения с помощью карт Карно полученные логические выражения, используемые для управления входами “J” и “К”, выглядят J4 = Q1 Q2 Q3 ; K4 = Q1 J3 = Q1 Q2; K3 = Q1 Q2; J2 =  Просмотр столбцов J1 и К1 в табл. 3.2 показывает, что все значения либо “~“, либо “1”. Так как безразличные состояния могут также участвовать в процессе упрощения, то все клетки карты Карно для J1 и К1 оказываются заполненными символами “~“, “1” и “a“. Следовательно, J1 = K1 = 1 На рис. 3.40 показана схема двоично-десятичного синхронного счетчика. Если счетчик из-за какой-либо неисправности окажется в одном из запрещенных (неиспользуемых) состояний, то его работа может быть прервана специальным сигналом и также может быть подан сигнал тревоги о неисправности в схеме счетчика. Обнаружить это позволяет схема, реализующая выражение, описывающее функцию неиспользуемых состояний fн = Q2 Q4 + Q3 Q4 . На рис. 3.41 показано, как эта схема используется для формирования цепи аварийной сигнализации и генерации блокирующего сигнала синхронизации.  Выражение , описывающее блокирующий сигнал синхронизации, имеет вид

Следовательно, когда fн = 1, то С’ = 0, и синхроимпульсы будут отсутствовать до тех пор, пока счетчик не выйдет из запрещенного состояния. Из схемы формирования блокирующего сигнала синхронизации следует, что логика её функционирования ориентирована на то, чтобы исключить возможность появления неиспользуемых комбинаций выходных сигналов. Действительно, в коде числа двоично-десятичного счетчика отсутствуют комбинации 0110, 0011, следовательно, их появление свидетельствует о неиспраности системы. Временные диаграммы счетчика (рис. 3.40), заданного графом переходов (рис. 3.38) и таблицей переходов 3.2, приведены на рис. 3.42.  Из рис. 3.42 следует, что все изменения состояний триггеров происходят во время формирования заднего фронта положительного импульса синхронизации. На временных диаграммах выходов Q1 . . . Q4 присутствуют двоичные цифры, характеризующие текущее состояние счетчика. |

JK-триггер

| 3.4. JK-триггер

Среди триггеров особое место занимают JK-триггеры, имеющие более широкие функциональные возможности. Упрощенная таблица (таблица управления) состояний JK-триг-гера содержит четыре строки (рис. 3.15, а). Из таблицы состояний видно, что для первых трех строк (наборов переменных) входы J и K играют роль входов S и R RS - триггера. Однако, для четвертого набора переменных, когда J=K=1 состояние триггера сильно отличается от состояния RS-триггера. Для RS-триггера - это запрещенная комбинация входных переменных, а в JK-триггере меняется (инвертируется) предыдущее состояние. JK-триггер можно синтезировать (построить) на базе двухступенчатого RS-триггера, для чего следует представить функциональную схему JK-триггера как совокупность КУ и синхронного RS-триггера (рис. 3.15, б).

Для получения логических выражений (характеристических уравнений) функций R и S комбинационного устройства необходимо построить совмещенную таблицу состояний JK и RS - триггеров (рис. 3.16, а). Из полученных выражений для S и R (рис. 3.16, б) следует, что для построения JK-триггера из двухступенчатого RS-триггера потребуется два элемента конъюнкции (на два входа каждый). Схема, полученная путем синтеза JK-триггера, приведена на рис. 3.17, а. Обозначение JK-триггера на функциональных схемах приведено на рис. 3.17, б.

×

Рис. 3.17. Синтезируемая схема а) и графическое обозначение б) JK - триггера

Выпускаемые промышленностью ИМС JK-триггеры могут иметь несколько входов (до трех) J и такое же количество входов K, объединенных схемами конъюнкций (рис. 3.18).

Рис. 3.18. Схемное обозначение ИМС JK – триггера, выпускаемого промышленностью Как следует из рис. 3.18, выпускаемые промышленностью JK-триггеры в виде интегральных микросхем также имеют асинхронные входы установки “0” и “1”(R и S входы, соответственно).

|

Понятие последовательностного автомата

| 3.1.

Понятие последовательностного автомата

Последовательностные цифровые устройства часто называют последовательностными схемами, последовательностными автоматами, дискретными автоматами с памятью, многотактными автоматами. Кроме комбинационных устройств, рассмотренных в предыдущей главе, существует класс цифровых устройств, в которых при одинаковых воздействиях на входе, на выходе автомата могут возникать различные выходные состояния. Состояние выхода такого устройства зависит не только от того, какие сигналы присутствуют на его входах в данный момент времени, но и от того, какие последовательности сигналов поступали на входы устройства в предшествующие моменты времени, т.е. как говорят, автомат помнит свою предысторию и хранит ее в памяти. Поэтому такие устройства называют последовательностными или многотактными автоматами. Для описания последовательностного автомата с памятью, помимо состояний входов X(t) и выходов Y(t), необходимо также знать состояние памяти автомата, как говорят, его внутреннее состояние S(t). В общем виде, последовательностный автомат рассматривается состоящим из двух частей: комбинационного устройства (КУ) и памяти, состоящей из элементов памяти (ЭП) (рис. 3.1). В качестве элементов памяти могут быть применены как однобитовые элементы памяти (различные типы триггеров), так и многобитовые (многоразрядные) цепочки триггеров. Функционирование (т.е. изменение состояния устройства) многотактного автомата происходит в дискретные моменты времени, ход которого обозначается натуральными числами t = 1, 2, 3 и т.д. В каждый момент дискретного времени t автомат находится в определенном состоянии S(t), воспринимает через входы соответствующую данному моменту комбинацию входных переменных X(t), выдает на выходах некоторую функцию выхода Y(t), определяемую как Y(t) = f (S(t),X(t)), и переключается в новое состояние S(t+1), которое определяется функцией переходов j как S(t+1)= j ( S(t),X(t)). Закон функционирования последовательностных автоматов может задаваться в виде уравнений, таблиц и графов. Под законом функционирования понимается совокупность правил, описывающих последовательность переключения состояний автомата и последовательность выходных сигналов в зависимости от последовательности поступления входных сигналов.

ЭП часто реализуется на основе бистабильных ячеек (БЯ). ЭП бывают: динамические, статические и квазидинамические. Наибольшее распространение получили первых два вида: статические и динамические. Статические ЭП реа- лизуются на БЯ. Динамические ЭП строятся, используя свойство хранения заряда между затвором и истоком полевых транзисторов МДП структуры. БЯ - является простейшим типом триггера, реализованного с помощью элементов базиса И - НЕ или ИЛИ - НЕ с соответствующими обратными связями и позволяет хранить один бит цифровой информации (бит - единица цифровой информации, соответствующая одной логической “1” или логическому “0”). Триггер - это последовательностная схема с двумя состояниями, каждое из которых при опреленных условиях на входах поддерживается постоянным (т.е. стабильным). Каждому из этих состояний ставится в соответствие логическое значение, которое “хранит” триггер (если на выходе триггера высокий уровень напряжения - “1” и “0” - в противном случае). Таким образом, в последовательностной схеме для представления значений каждой переменной, которую нужно хранить для использования в настоящем или в будущем, следует использовать отдельный триггер. Совокупное состояние последовательностной схемы, запоминающее устройство которой реализовано на триггерах, представляет собой просто комбинацию состояний этих триггеров. Вообще говоря, у триггера должна быть по крайней мере одна выходная линия, представляющая логическое значение, соответствующее состоянию триггера. Когда на выходной линии логическая 1, говорят, что триггер установлен, в противном случае говорят, что триггер сброшен. Триггер имеет несколько входных линий, сигналы на которых (вместе с текущим состоянием триггера) определяют следующее состояние триггера. От функций входных линий зависит тип триггера. Простейшим триггером является RS - триггер. RS - триггер имеет два входа и два выхода. Входы и выходы триггера имеют свои обозначения. Один из входов триггера называется установочным входом и обозначается буквой S (от английского set - установить), а другой - входом сброса и обозначается буквой R ( от reset - сбросить). Триггер (рис. 3.2) имеет два симметричных выхода. На одном выходе (условно называемом прямым выходом) сигнал представляется без отрицания (выход Q), а на другом - с отрицанием (`Q - инверсный выход). По способу подачи переключающих сигналов (в зависимости от комбинации входных сигналов) триггеры делятся на RS, MS, D, JK, T - триггеры.  Рис. .3.2. Графическое обозначение RS - триггера Триггеры бывают переключающимися уровнем и фронтом тактирующего сигнала ( импульса ). Несмотря на большое разнообразие триггеров, практически все триггеры строятся на базе RS -триггеров. |

Регистры

| 3.6.

Регистры

Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK -триггеров. По способу приема и выдачи информации регистры делятся на следующие группы: с параллельным приемом и выдачей (рис. 3.25, а); с последовательным приемом и выдачей (рис. 3.25, б); с последовательным приемом и параллельной выдачей (рис. 3.25, в); с параллельным приемом и последовательной выдачей (рис. 3.25, г); комбинированные, с различными способами приема и выдачи (рис. 3.25, д) и реверсивные. Регистры хранения (пямяти). Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0 . . . Dm новой цифровой комбинации (информации) при поступлении определен-